IN THE NEWS TODAY

OUR PRODUCTS: THE SIGNAL CHAIN

Eurolink Systems provides its clients with only state-of-the-art products and systems, covering the whole signal processing chain, as described below: from RF to Ethernet.

THE MARKETS WE OPERATE IN

Eurolink Systems supplies solutions as embedded systems, rugged servers, storage, peripherals, networking, data acquisition, monitors, single boards computers ( SBC’s ), analog/digital/serial I/O boards, Radio Frequency/Microwave and much more in all the form factors used by the industry for the following markets:

THE E-SOLUTIONS COMPANY

Eurolink Systems is an European Company specialized in Services and Distribution with Added Value of Hardware, Software,

and Data Management Solutions for the following Business Unit’s (BU’s):

AWARDS EARNED

In 2019, and in 2020 the most important Italian Financial Newspaper “IlSole24Ore” anwarded Eurolink Systems as one of the top 350 Italian Companies.

Leonardo, the most important Italian defence and aerospace company, chose us to be part of their Elite Lounge project. Only 22 high quality companies, selected between a group of 2800 suppliers are part of the program.

SUCCESS STORIES

Did you know that…

more than 250 worldwide flight and sea destinations are reached thanks to the processing power and data analisys capabilities provided by Eurolink Systems…

during flights, radars looking after safety on your route are Eurolink Systems solutions inside…

when you ride on a subway train, Eurolink Systems provided electronics for your safety…

the Italian Navy entrusts Eurolink Systems with safety and monitoring solutions fr their radars, sonars, C4 system performances…

international research labs adopted cutting edge technologies in data processing provided by Eurolink Systems…

armies in several theaters of operation are employing UGVs and UAVs provided by Eurolink Systems for their safety…

We are taking care of you, your customers and citizens 24/7, day by day, 365 days per year, never leaving your side along the entire lifecycle of our products and solutions;

Eurolink Systems is Your Partner in Business from Radio Frequency to Ethernet through Your robotics solutions

OUR KEY PARTNERS

Eurolink Systems partnered with many companies to provide his products and services.

Following you can find any companies on his partners portfolio:

GENERAL STANDARDS CORPORATION

ISOLUTION INC. mmWave CABLE, 5cG, Antenna, connector, RF Modules

LAMBDA

See more…

uAvionix

CONTACT EUROLINK SYSTEMS TODAY

Please don’t hesitate to contact us for questions, information or quotations. We’ll be glad to answer you soon.

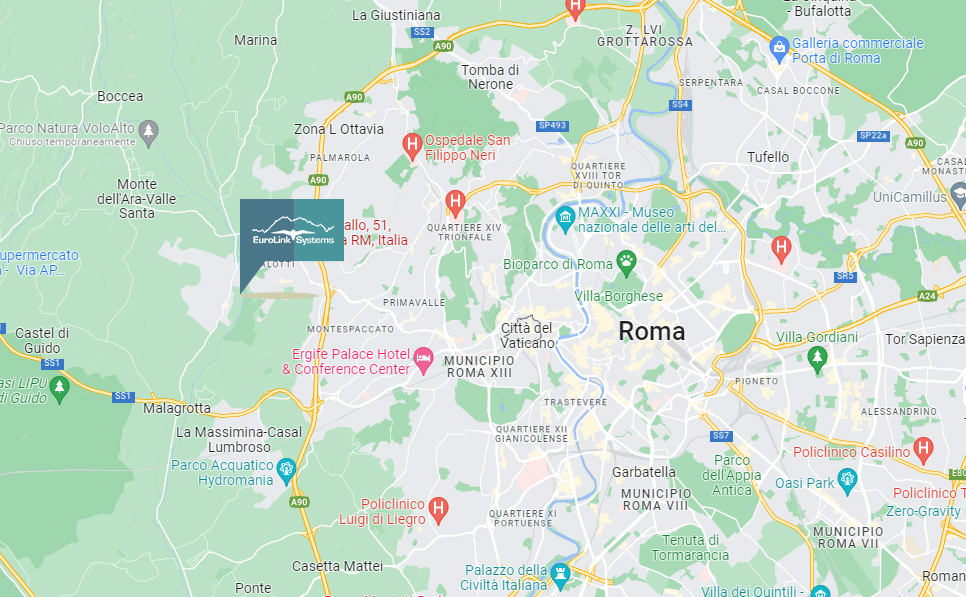

Eurolink Systems HQ

Via Piedicavallo, 51, 00166 Roma RM

Phone/FAX: +39 06 61914001

E-mail: [email protected]